# DESCRIPTION

The MP6910 is a fast turn-off intellig ent rectifier for Flyback converters that combines a 100V power switch that repla ces diode r ectifiers for high efficiency. The chip regulates the forward voltage drop of the internal power switch to about 70mV and turns it off before the voltage goes negative.

## FEATURES

- Supports DCM and Quasi-Resonant Flyback converter

- Integrated 10mΩ 100V Power Switch

- Compatible with Energy Star, 1W Standby Requirements

- V<sub>DD</sub> Range From 8V to 24V

- Max 400kHz Switching Frequency

- Supports High-side and Low-side Rectification

- Power Savings of Up to 1.5W in a Typical Notebook Adapter

## **APPLICATIONS**

- Industrial Power Systems

- Distributed Power Systems

- Battery Powered Systems

- Flyback Converters

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

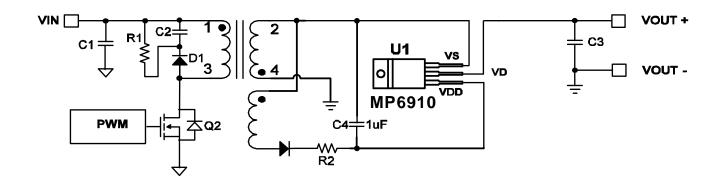

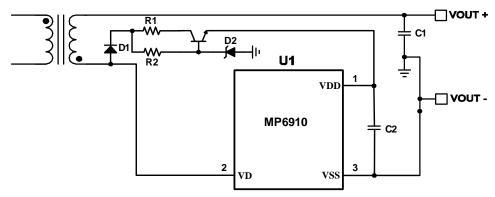

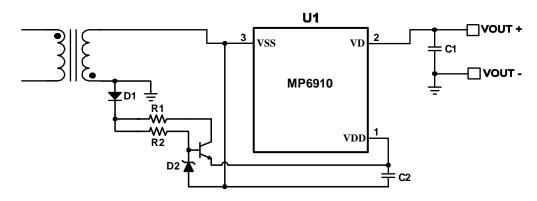

## TYPICAL APPLICATION

## **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |  |  |

|--------------|---------|-------------|--|--|

| MP6910DZ     | TO220-3 | MP6910DZ    |  |  |

\* For RoHS Compliant Packaging, add suffix -LF; (e.g. MP6910DZ-LF)

# PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| $V_{DD}$ to $V_S$ 0.3' $V_D$ to $V_S$ 0.7V Maximum Operating Frequency        | to +100V |  |  |  |

|-------------------------------------------------------------------------------|----------|--|--|--|

| Maximum Operating Frequency<br>Continuous Drain Current ( $T_c=25^{\circ}C$ ) |          |  |  |  |

| Continuous Drain Current $(T_c=100^{\circ}C)$                                 | 15A      |  |  |  |

| Maximum Power Dissipation <sup>(2)</sup>                                      | 2.7W     |  |  |  |

| Junction Temperature                                                          | 150°C    |  |  |  |

| Lead Temperature (Solder)                                                     |          |  |  |  |

| Storage Temperature55°C t                                                     |          |  |  |  |

| Recommended Operation Conditions <sup>(3)</sup>                               |          |  |  |  |

| $V_{DD}$ to $V_{S}$                                                           |          |  |  |  |

| Operating Junction Temp. (T <sub>J</sub> )40°C t                              | o +125°C |  |  |  |

# Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

### Notes:

- 1) Exceeding these ratings may damage the device.

- 2)  $T_A$ =+25°C. The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated b y  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause ex cessive die temp erature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitr y pr otects the device from permanent damage.

- The device is not guarant eed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

### $V_{DD} = 12V$ , $T_A = +25^{\circ}C$ , unless otherwise noted.

| Parameter                                                        | Symbol<br>V <sub>(BR)DSS</sub> | Conditions                                | Min  | <b>Typ</b><br>110 | Max  | Units<br>V |

|------------------------------------------------------------------|--------------------------------|-------------------------------------------|------|-------------------|------|------------|

| Drain-to-Source Breakdown Voltage                                |                                |                                           |      |                   |      |            |

| V <sub>DD</sub> Voltage Range                                    |                                |                                           | 8    |                   | 24 V |            |

| V <sub>DD</sub> UVLO Rising                                      |                                |                                           | 5.0  | 6.0               | 7.0  | V          |

| V <sub>DD</sub> UVLO Hysteresis                                  |                                |                                           | 0.8  | 1.2               | 1.5  | V          |

| Operating Current                                                | I <sub>CC</sub>                | F <sub>sw</sub> =100kHz                   | 4.5  |                   | 8    | mA         |

| Light-Load Mode Current                                          |                                |                                           |      | 260               | 360  | μA         |

| CONTROL CIRCUITRY SECTION                                        |                                |                                           |      |                   |      |            |

| V <sub>SS</sub> –V <sub>D</sub> Forward Voltage                  | V <sub>fwd</sub>               |                                           | 55   | 70                | 85   | mV         |

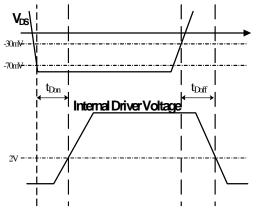

| Turn-on Delay <sup>(5)</sup>                                     | T <sub>Don</sub>               |                                           |      | 200               |      | ns         |

| Turn off Threshold $(V_{SS}-V_D)^{(5)}$                          |                                |                                           |      | 30                |      | mV         |

| Turn-off Delay <sup>(5)</sup>                                    | T <sub>Doff</sub>              | V <sub>D</sub> =V <sub>SS</sub>           |      | 30                | 45   | ns         |

| Minimum On-time <sup>(5)</sup>                                   | T <sub>MIN</sub>               |                                           |      | 1.6               |      | μs         |

| Light-load-enter Delay                                           | $T_{LL-Delay}$                 |                                           |      | 120               |      | μs         |

| Light-load-enter Pulse Width                                     | T <sub>LL</sub>                |                                           |      | 2.2               |      | μs         |

| Light-load-enter Pulse Width<br>Hysteresis                       | T <sub>LL-H</sub>              |                                           |      | 0.2               |      | μs         |

| Light-load Mode Exit Pulse Width<br>Threshold (V <sub>DS</sub> ) | $V_{LL-DS}$                    |                                           | -400 | -250              | -150 | mV         |

| POWER SWITCH SECTION                                             |                                |                                           |      |                   |      |            |

| Single Pulse Avalanche Current <sup>(6)</sup>                    | I <sub>AS</sub>                |                                           |      | 66                |      | А          |

| Single Pulse Avalanche Energy <sup>(6)</sup>                     | E <sub>AS</sub>                |                                           |      | 597               |      | mJ         |

| Drain-Source On-State Resistance                                 | R <sub>DS(ON)</sub>            | V <sub>GS</sub> =10V, I <sub>D</sub> =20A |      | 10.2              |      | mΩ         |

| Input Capacitance                                                | C <sub>iss</sub>               | V <sub>DS</sub> =40V, f=1MHz              |      | 5110              |      | pF         |

| Output Capacitance                                               | C <sub>oss</sub>               |                                           |      | 334               |      | pF         |

| Reverse Transfer Capacitance                                     | C <sub>rss</sub>               |                                           |      | 150               |      | pF         |

| DRAIN-SOURCE DIODE CHARACTE                                      |                                |                                           |      |                   |      |            |

| Reverse Recovery Time                                            | t <sub>rr</sub>                |                                           |      | 81                |      | ns         |

| Diode Reverse Change                                             | Q <sub>rr</sub>                |                                           |      | 190               |      | nC         |

#### Notes:

Guaranteed by Design and Characterization.

Starting T<sub>J</sub>=25°C, L=0.3mH

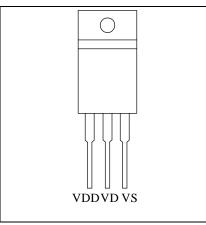

## **PIN FUNCTIONS**

| Pin # | Name | Description                                |

|-------|------|--------------------------------------------|

| 1 VDD |      | Supply Voltage                             |

| 2     | VD   | FET Drain                                  |

| 3     | VS   | FET Source, also used as reference for VDD |

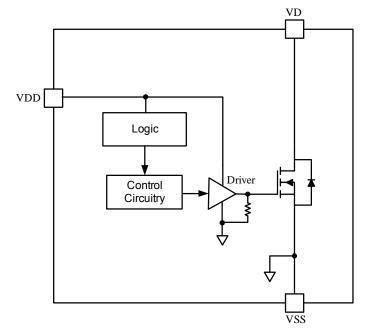

# **BLOCK DIAGRAM**

Figure 1—Function Block Diagram

# OPERATION

The MP691 0 supports operation in DCM an d Quasi-Resonant Flyback converters. The control circuitry con trols the gate in forward mode an d will turn the gate off when the MOSFET current is fairly low.

### Blanking

The control circuitry contains a blanking function. When it pulls the integrate Mosfet on/off, it makes sure that the on/off state at least lasts for some time. The turn on blanking time is ~1.6us, which determines the minimum on-time. During the turn on blanking period, the turn off threshold is n ot totally blan ked, but changes t he thresho Id voltage to ~+50mV (i nstead of -30mV). Th is assures that the part can always be turned off even during the turn on blanking p eriod. (Albeit slower)

### Under-Voltage Lockout (UVLO)

When the VDD is below UVLO threshold, the part is in sleep mode and the integrate d Mosfet i s never turned on.

### **Basic Operation**

The basic operations of flyback converter with MP6910 are:

### • Turn On Phase

The switch current will f irst flow thr ough the body diode of the integrate Mosfet, which generates a negative Vds acro ss it (<-500mV). The voltage is much smaller than the turn on threshold of the control circuitry (-70mV), which turns o n the integrat e Mosfet after 200ns turn on delay (defined in Fig.2).

### Conducting Phase

When the integrated Mosfet is turned on, Vds becomes to rise according to its on resistance, as soon as Vds rises above the turn on threshold (-70mV), the control circuitry stops pulling up the gate driver, which leads the driver voltage of the integrate Mosfet dropped to larger the on resistance to ease the rise of Vds. By doing that, Vds is adjusted to be around -70mV even when the current through the switch is fairly small, this funct ion can make the internal driver voltage f airly low when the mosfet is turned off to fast the turn off speed (this funct ion is st ill a ctive during turn on blanking pe riod which means the integrate mosfet could still be turned off even with very small duty).

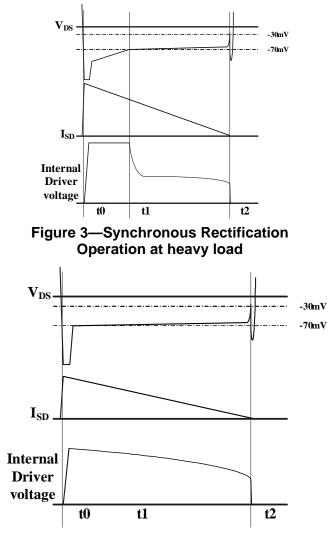

Fig.3 sho ws synchronous rectification operation at heavy load condition. Due to the high cu rrent, the in ternal driver voltage will be satu rated at first. After Vds goes to above -70 mV, driver voltage decreases to adjust the Vds to typical -70mV.

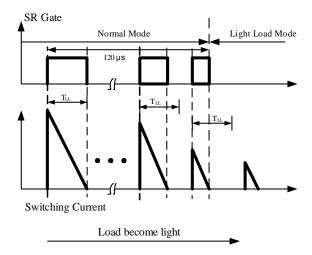

Fig.4 sho ws synchronous rectification operation at light load condition. Due to the low current, the driver voltage never saturates but begins to decrease as soon as the integrated mosfet is turned on and adjust the Vds.

### • Turn Off Phase

When Vds rises to trigger the turn off threshold (-30mV), the driver voltage of the switch is pulled to low after about 20ns turn off delay (d efined in Fig.2) by the control circuitry. Similar with turn-on phase, a 200ns blanking time is adde d after the switch is turned off to avoid error trigger.

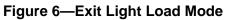

### Light-load Latch-off Function

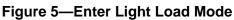

The gate driver of integr ate Mosfet in MP6910 is latched to save the d river loss at light-loa d condition to improve efficiency. T he light-loa denter pulse width T <sub>LL</sub> is internal f ixed (~2.2 µs). When synchronous power switch conductin g period keep s lower than T <sub>LL</sub> for lo nger than the light-load-enter delay (T <sub>LL-Delay</sub>), MP6910 enters light-load m ode and la tches off t he integrat e Mosfet (Fig.5 for detail).

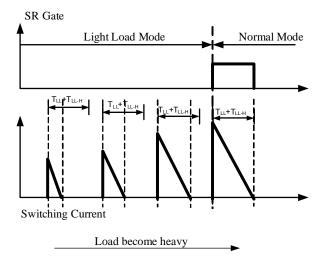

During light -load mode, MP6910 monitors the integrate Mosfet body diode conducting period by sensing V <sub>DS</sub> (when V <sub>DS</sub> exceeds the light-load mode exit pulse width threshold V <sub>LL-DS</sub>, MP6910 considers t he integrat e Mosfet body diode conducting time finishes). If the Mosfet bod y diode conduction time is lo nger t han T <sub>LL</sub>+T<sub>LL-H</sub> (T<sub>LL-H</sub>, light-load-enter pulse width hysteresis), the light-load mode is finished and the integrate

Mosfet of MP6910 is unlatched to restart t he synchronous rectification (Fig.6 for detail).

### **Typical System Implementations**

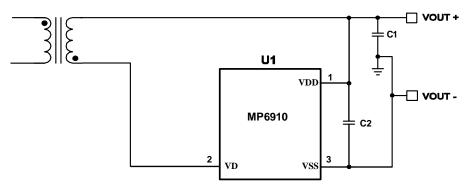

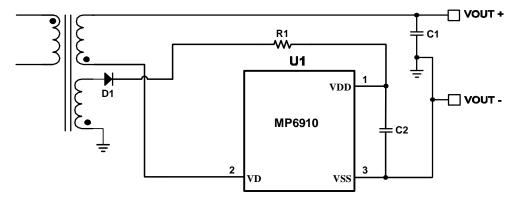

Fig.7 shows the typical system i mplementation for the IC supply derived from o utput voltage, which is available in low-side rectification and the output voltage is recommended to be in the VDD range of MP6910 (from 8V to 24V).

If output v oltage is o ut of the  $V_{DD}$  range of MP6910 or high-side r ectification is used, it is recommended to use a n auxiliary winding from the power transformer for the IC supply, which is shown in Fig.8 and Fig.9.

There is another non-auxiliary win ding solution for the IC supply, which uses an external LDO circuit from the secondary transformer windin g. See fig.10 and fig.1 1, compared with using auxiliary winding for IC supply, this solution has a bit higher p ower loss which is d issipate on t he LDO circuit especially when the secondary winding voltage is high.

Figure 2—Turn on and Turn off delay

Figure 4—Synchronous Rectification Operation at light load

Figure 7—IC supply derived directly from output voltage

Figure 8—IC supply derived from auxiliary winding in low-side rectification

Figure 9—IC supply derived from auxiliary winding in high-side rectification

Figure 10—IC supply derived from secondary winding in low-side rectification

Figure 11—IC supply derived from secondary winding in high-side rectification

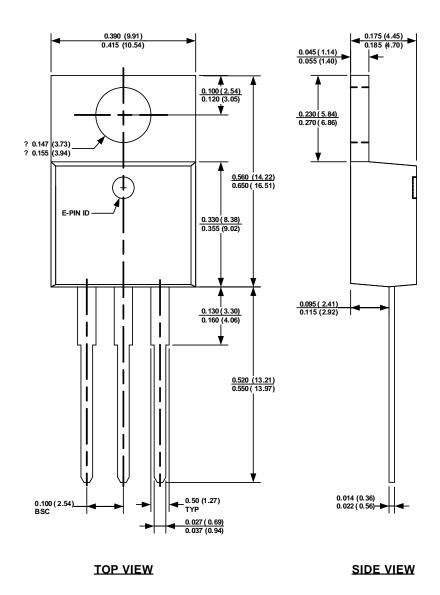

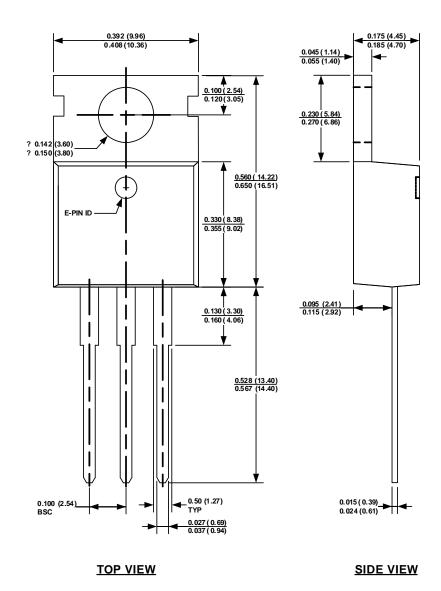

## **PACKAGE INFORMATION**

#### NOTE:

1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASHPROTRUSIONS OR GATE BURRS 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS 4) DRAWING CONFORMS TO JEDEC TO220 6) DRAWING IS NOT TO SCALE

6) DRAWING IS NOT TO SCALE

#### NOTE:

1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASHPROTRUSIONS OR GATE BURRS 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS 4) DRAWING CONFORMS TO JEDEC TO220 6) DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Int ellectual Property rights are n ot infringed u pon when integrating MPS product s into any application. MPS will not assume any legal responsibility for any said applications.